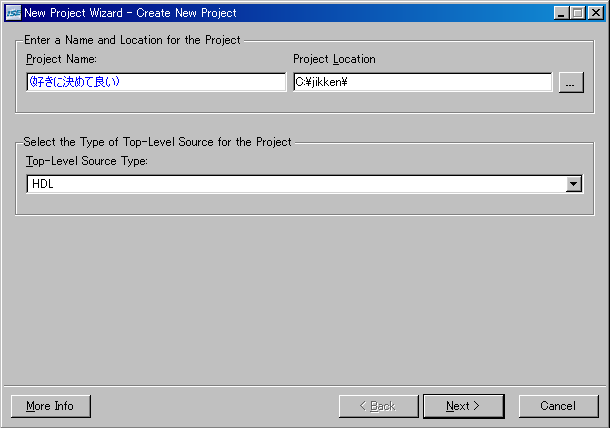

(a)Create New Project

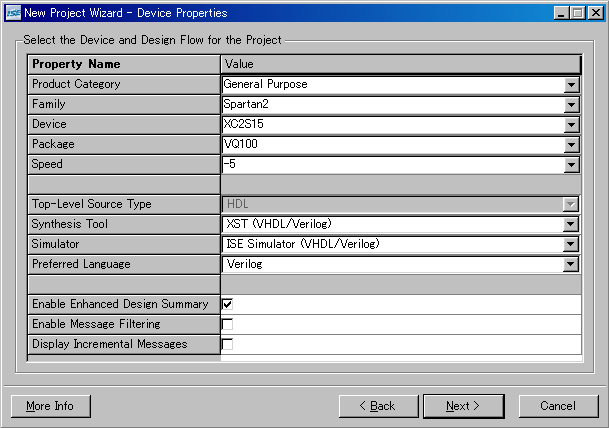

(b)Device Properties

図1: プロジェクトの新規作成

今週は HDL を用いて設計した回路を FPGA 上で実現するための流れを学習する。

最初に、LED とスイッチを単に接続した回路 (つまり、スイッチを ON にしている間のみ LED を ON にする回路) を作成する。本実習では Xilinx ISE Project Navigator を用いる。なお、本ページの資料はバージョン 9.2i を用いて作成されている。他のバージョンを使用する場合は、適宜、読み替えられたい。

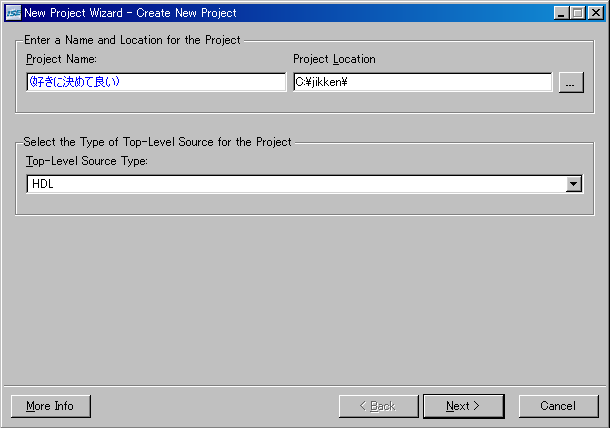

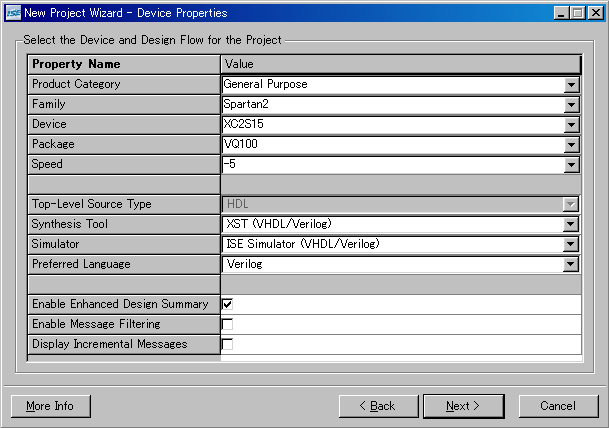

Project Navigator では VC などと同様に、一連の設計をプロジェクトという単位でまとめて扱う。まずはプロジェクトを新規作成する。Project Navigator を起動されたい。Project Navigator は直前の状況をだいたい記憶している(完全ではない)。よって、起動時の状態は人によって異なるであろうが、気にしないでいただきたい。File → New Project を選ぶ。次に出現するダイアログに対し、図1 のように応対する。3個目以降のダイアログに対しては、全て Next または Finish を選ぶこと。

(a)Create New Project

(b)Device Properties

図1: プロジェクトの新規作成

次に、回路を HDL で記述する。なお、本実習では Verilog-HDL を用いる。Verilog-HDL については学部の実験II-6 でも扱った。実験テキスト等はサイト上に残してあるので、適宜参照されたい。

Verilog-HDL ではひとまとまりの回路をモジュールと呼ぶ。C言語における関数を想像すると分かり易い。まずはモジュールを作成する。Project → New Source, Verilog Module を選び、適当なファイル名 (拡張子は不要) をつける。図2のようなダイアログが現れるので、Port Name と Direction を図のように入力されたい。残りのダイアログについては全て Next または Finish を選ぶこと。

図2: Define Module

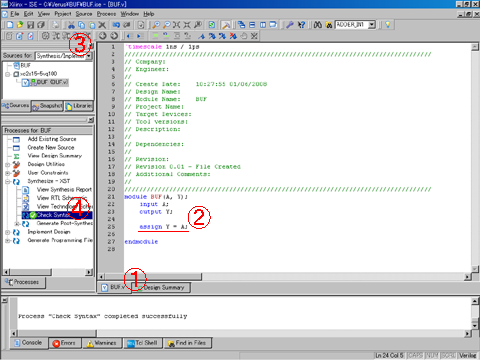

次に回路を記述する。図3 (1) のタブから作成したソースファイルを選択すると、図3 (2) に示すようなソースファイルが現れる。図3 (2) 下線部や図4 に示すように assign 文を追加されたい。

図3: モジュール入力画面

module モジュール名(A, Y);

// モジュール宣言、モジュール名に続き、入出力信号を括弧内に列挙している

input A; // 入力信号を宣言している

output Y; // 出力信号を宣言している

assign Y = A; // 左の通りに記述を追加せよ。

// 出力 Y と入力 A を直接つなぐという意味

endmodule // モジュールの終わりを宣言している

|

図4: 作成するモジュール

次に文法チェックをする。図3 (3) Sources for が Synythesis/Implementation になっていることを確認し、図3 (4) Synthesize - XST → Check Syntax を選ぶ。エラーがあれば修正する。

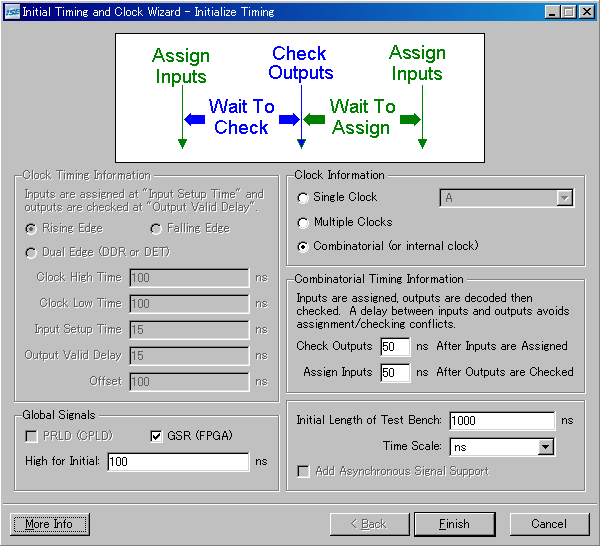

次にシミュレーション実験を行う。まずシミュレーション時に回路に与える入力波形を作成する。Project → New Source, Test Bench WaveForm を選び、適当なファイル名をつける。あとは大体 Next または Finish を選んでいけばよい。ただし、ダイアログ Initialize timing について、Clock Information が Single Clock になっている場合は、これを図5に示すように Combinational (or internal clock) に直すこと。

図5: Initialize timing

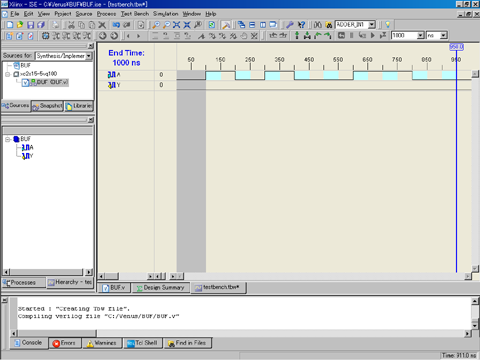

図6に示すような波形図エディタが起動するので、入力信号 A について、適当な波形図を作成すること。

図6: 波形図エディタ

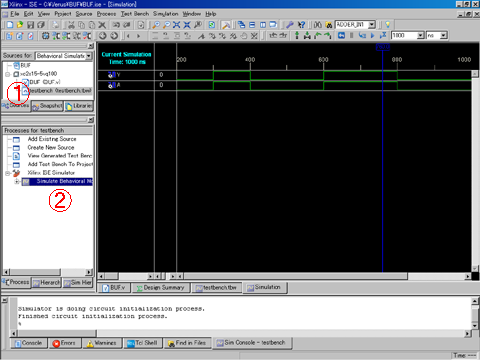

図7 (1) Source for を Behavioral Simulation にし、.tbw ファイルが選択されていることを確認する。図7 (2) のタブをProcesses とし、Simulate Behavioral Module を選ぶ。正しくシミュレーション結果が表示されていることを確認する。表示直後はズームがあっていないことがあるので Simulation Zoom からズームを調整すること。予想通りのシミュレーション結果が得られたら次に進む。

図7: シミュレーション結果

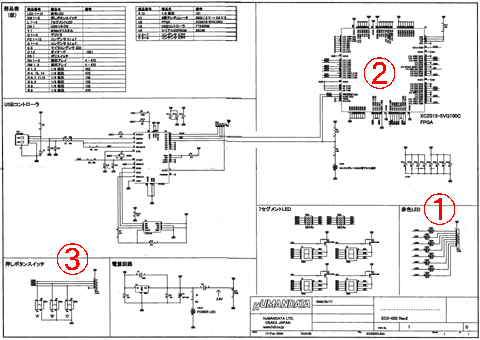

次に入出力ピンの割り当てを行う。配布したボードに注目されたい。LED が 8個、スイッチが3個並んでいることが分かる。配布した回路図を参照されたい。図8 (1) のように、赤色 LED 8個についてアノードが抵抗を経由し電源 V33 に接続され、カソードがピン LED0 ~ 7 に接続されているのが分かる。ここでは LED0 を点灯させることにする。図8 (2)、FPGA の入出力ピンを確認されたい。 LED0 は 68 の入出力ピンであることがわかる。図8 (3)、押しボタンスイッチについて、電源 V33、抵抗、押しボタンスイッチ、グランド GND が直列に接続されており、抵抗と押しボタンスイッチの間からピン PSW0 ~ 2 に出力されているのが分かる。ここでは PSW0 を用いることにする。図8 (2) から PSW0 は 15 の入出力ピンであることが分かる。

図8: FPGA 回路図 (マニュアルより引用)

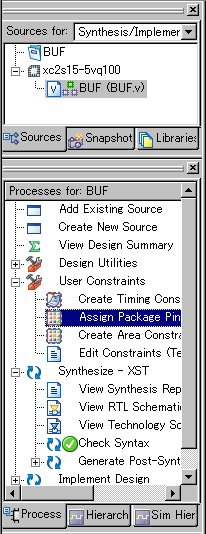

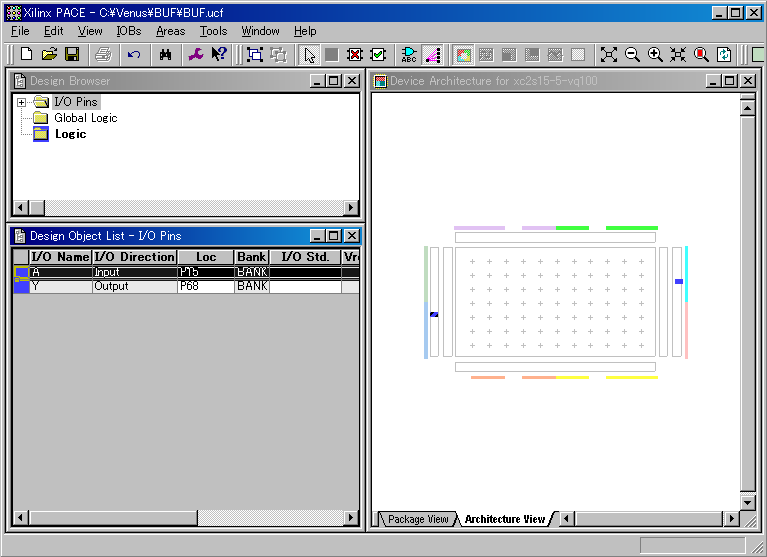

Project Navigator に戻られたい。図9 (1)、Source for Synthesis/Implementation とし、図9 (2) User Constraints → Assign Package Pin を選ばれたい。図(10) に示す Xilinx PACE が起動されたはずである。図10 に示すように Design Object List - I/O Pins の表中、Loc の列をそれぞれ、P15, P68 と入力されたい。ここで、P15, P68 はそれぞれ、15, 68 の入出力ピン、つまり LED0, PSW0 を意味する。入力したら Xilinx PACE を終了する。 ucf ファイルは保存する。

図9: Assign Package Pin

図10: Xilinx PACE

図8 (2) のウィンドウ中、Generate Programming File を選ぶことにより、論理合成を行う。合成に成功した場合、プロジェクトのディレクトリ内に拡張子が bit なるファイルが作成されているのが確認できるはずである。これが FPGA のコンフィギュレーションデータである。

最後にコンフィギュレーションデータをFPGA にダウンロードする。FPGA を USB ポートに接続する。c:\jikken 下に BitCfg という実行ファイルがあるので、これを起動する。File から、先ほど確認したコンフィギュレーションデータを選択し、Download する。これで作業は完了である。ボード上のスイッチ C を押したとき、右端の LED が点灯するのを確認できるはずである。

難波 一輝 (助教・伊藤・北神・難波研究室)

工学部1号棟4階409号室、内線3255、043-290-3255、namba@ieee.org