今週は Project Navigator 内で行われている論理合成と配置配線について、その結果を見る。なお、今週は60分目から20分程度のディスカッションを設ける予定である。そのつもりで実習を進めること。

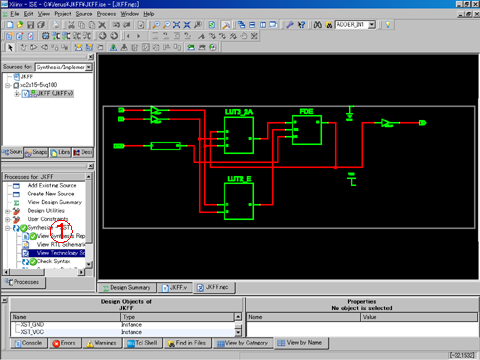

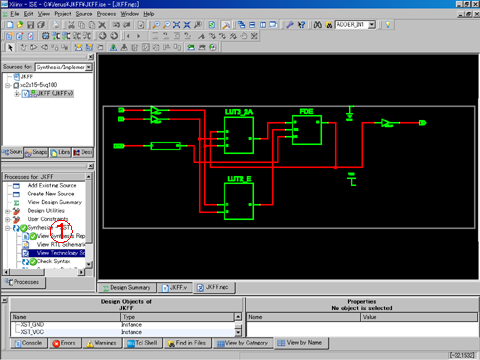

先週までに作成した回路、または自分で作成した回路について、図1 (1) Synthesize - XST → View RTL Schematic, View Technology Schematic を選ぶ。それぞれ、単に Verilog 文法を解釈した回路図と、FPGA 用に合成して得られる回路図が表示される。図1 の例は、JK フリップフロップを合成して得られる回路図である。この FPGA は JK フリップフロップをもっていない。そこで、2個のプログラマブルなゲート (LUT) と Dフリップフロップにより JKフリップフロップを実現している。

図1: 論理合成結果

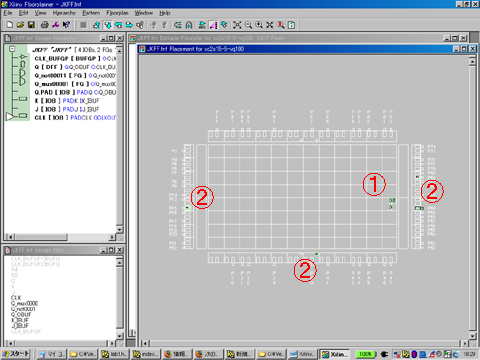

図1 (1) のウィンドウ中 Implement Design → Place & Route → View/Edit Placed Design を選ぶ。Fllorplanner が起動し、配置結果を見ることができる。図2 は図1 の JKフリップフロップに対し、配置を行った結果である。図2 (1) に、2個の LUT と 1個のDフリップフロップが配置されているのが分かる。また 図2 (2) には使用する入出力ピンが示されている。

図2: 配置結果

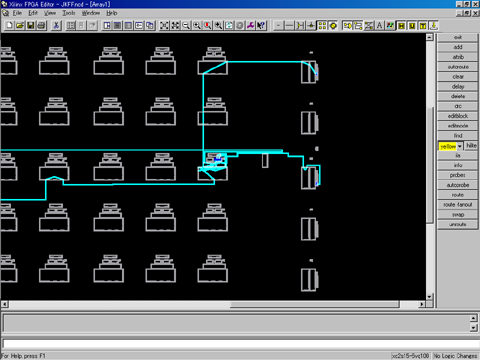

図1 (1) のウィンドウ中 Implement Design → Place & Route → View/Edit Routed Design を選ぶ。FPGA Editer が起動し、配線結果を見ることができる。図3 は図1 の JKフリップフロップに対し、配線を行った結果 (拡大図) である。ズームを調整しながら確認されたい。なお、箇所によっては、ダブルクリックによりさらに詳細な図を見ることもできる。

図3: 配線結果

難波 一輝 (助教・伊藤・北神・難波研究室)

工学部1号棟4階409号室、内線3255、043-290-3255、namba@ieee.org