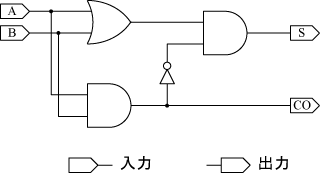

図1. 半加算器の回路図

先週の実験では、紙上に回路図を書いて回路の設計を行った。しかし、GPU (Graphics Processing Unit) など近年の巨大なシステムを紙上で設計することは困難であり、コンピュータ上で設計することが一般的である。今週は、近年の回路設計技術に対する理解を深めるため、Windows ツール、Xilinx ISE WebPACK を用いて回路設計を行う。また、設計した回路をシミュレータ上で動作させる。

一般に集積回路の作製には時間がかかり、また大量生産を行わない限り非常にコストもかかる。そこで、特にシステムの試作段階や、少量生産しか行わないような場合には、FPGA (Field Programmable Gate Array) など論理回路をエミュレートできる回路が使用される。Xilinx は FPGA の大手メーカであり、ISE WebPACK は Xilinx の提供する FPGA デザインツールである。

Xilinx ISE WebPACK (以下、ISE と呼ぶ) は Xilinx のサイトから無料でダウンロード、利用することができる。ただし、自宅で自習しようと考えている者は、インストールが割と大変であることに注意して欲しい。あと、同サイトでは同時に ISE Design Suite という有償ツールの無料評価版も配布しているので注意されたい。

これから ISE 上での基本的な回路設計ついて説明する。題材として半加算器を用いる。半加算器は1ビットの足し算を行う回路である。具体的に入力信号線 A と B の値を足して得られる値を出力信号線 S に返す。また、桁上げ (キャリー) を出力信号線 CO に返す。半加算器の回路図と真理値表をそれぞれ図1と表1 に示す。

図1. 半加算器の回路図

表1. 半加算器の真理値表

| A | B | CO | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

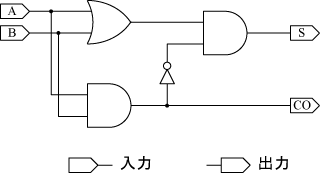

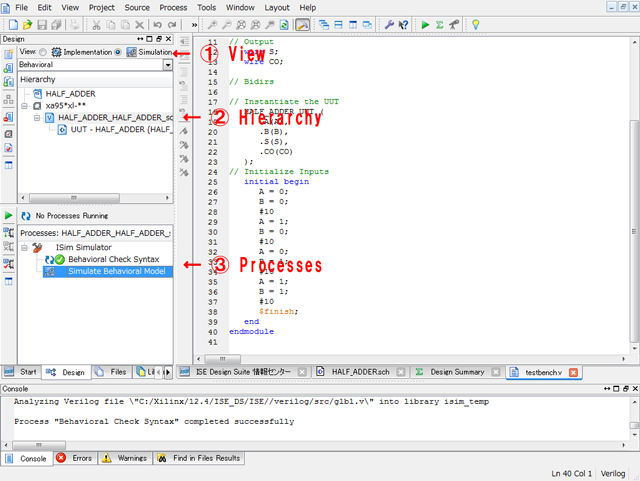

"すべてのプログラム → Xilinx ISE Design Suite 12.4 → ISE デザインツール → Project Navigator" でISEを起動する。図2のようなソフトが起動する。ISE は (1)ワークスペース、(2)パネル (3)トランスクリプト の3領域を持つ。

図2. ISE 起動直後の画面

C言語のプログラミングを想像して欲しい。C言語では、システムの1部分または全体となるひとまとまりのプログラムを考え、これを関数と呼ぶ。同様に ISE ではシステムを構成するひとまとまりの回路をモジュール (module) と呼ぶ。ISE では、モジュール1個につき、ファイル1個を生成する。またその他、多数の制御用ファイルを作成する。一連の回路設計とこれら必要ファイルをプロジェクト(Project) と呼ばれる単位でまとめて管理している。

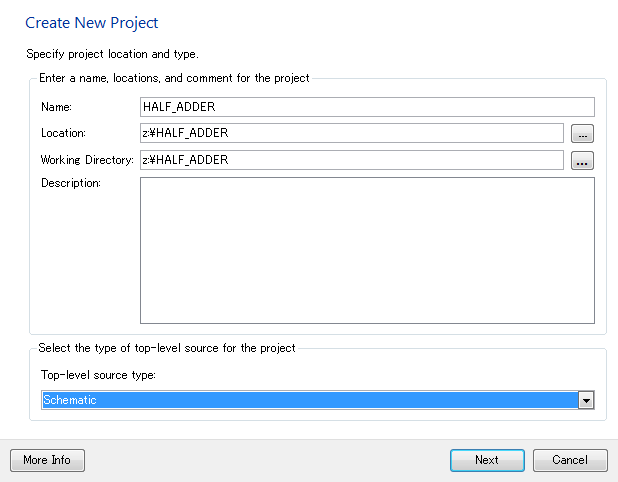

まずはプロジェクトを新規作成する。パネルが図2 のようになっていることを確認する。なっていない場合は直前に開いていたプロジェクトが残っているので、"File → Close Project" で閉じる。"File → New Project" を選ぶ。New Project Wizard が起動するので以下の通りに応える。

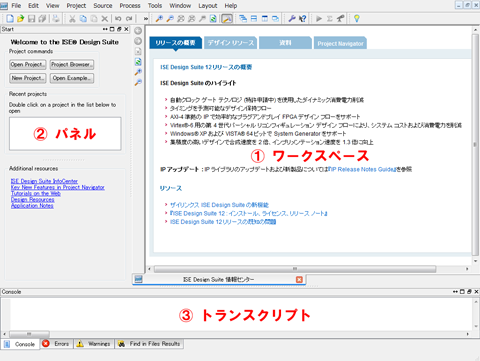

まず、図3 のようなダイアログが開く。Name には作成したいプロジェクトの名前を記入する。ここでは "HALF_ADDER" とする。 Top-level source type を "Schematic" にする。【注意】Project Location は c:\Users 下ではなく、Z ドライブ上に変更すること。C ドライブ上に作成したディレクトリ、ファイルは再起動時に削除される。

図3. New Project Wizard - プロジェクト名の設定

プロジェクト名は英数字およびアンダースコア "_" を用いることができる。ただし、1文字目には数字は許されない。日本語は用いることはできない。空白は用いることができない。大文字と小文字は区別されることと、されないことがある。どちらに解釈されても良いように名付ける必要がある。以降、モジュール名、信号線名など、様々な名前をユーザが名付けることになる。このとき、すべて同じ制約が適用される。

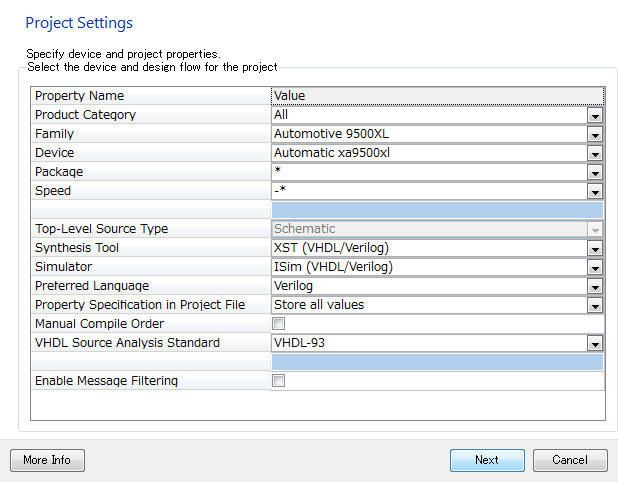

次に図4のようなダイアログが開く。ここでは細かなデバイス特性等を指定できる。図4の通りに答える。(おそらくデフォルトの通りである。)

図4. New Project Wizard - デバイスの設定

あとは全て Yes, Ok, Next, Finish など肯定的な返事をしながら進む。

なお、ISE は業務用であり、非常に癖が悪く、バグも多い。どうにも困ったときは、まずは "Project → Cleanup Project Files" としてみるとよい。それでもうまくいかない場合、プロジェクトの作成からやり直した方がはやい。

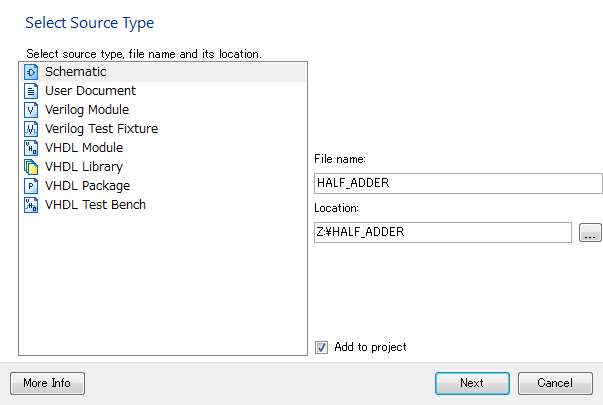

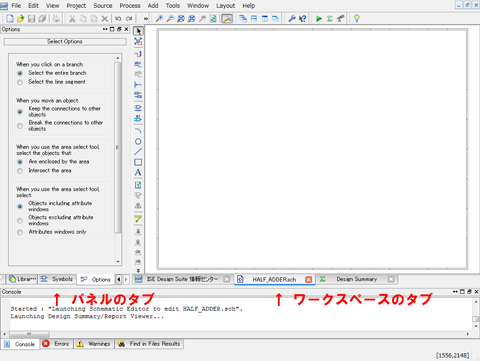

まずは "Project → New Source" とし、New Source Wizard を起動する。 図5 のようなダイアログが開くので、左側は "Schematic" (回路図の意味) とし、File Name に作成したいモジュール名を書く。ここでは "HALF_ADDER" とする。あとは全て肯定的に応答する。Schematic Editor が起動する。ワークスペースのタブ "HALF_ADDER.sch" を選択すると図6のような画面になる。これからワークスペース上に図1に示した半加算器の回路図を記述していく。

図5. New Source Wizard - 新規モジュールのタイプと名前の設定

図6. Schematic Editor

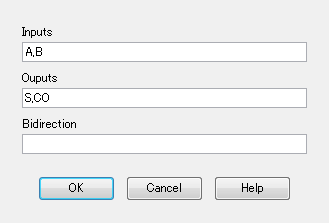

まずは入出力マーカを配置する。"Tools → Create I/O Markers" とする。図7のようなダイアログが開く。図1より、配置したい入力マーカは A, B である。そこで、Inputs には "A,B" と書く。同様に Outputs には "S,CO" と書き、配置したい出力マーカを指定する。

図7. 入出力マーカ作成

正しく入出力マーカが出現しているか確認して欲しい。文字が小さいのでズーム ("View → Zoom") を駆使しながら確認すること。

なお、"Tools → Create I/O Markers" は空の回路図に対してだけ実行できる。

次にゲートを配置する。まずは、パネルのタブを "Symbols" にする。図8のようなフォームが現れる。図1より、作成したいゲートは 2入力AND が 2個と、2入力OR, インバータ(NOTゲート)である。パネル中程 Symbols から配置したいゲート名を探し、選択する。選択モードからシンボルモードに移行するので、ゲートをワークスペース上にゲートを配置する。2入力AND, 2入力OR, インバータのシンボル名はそれぞれ "and2", "or2", "inv" である。Symbol Name Filter からシンボル名を絞りながら探すと速い。配置が気に入らない場合、"Edit → Select and Clear → Select Object(s)" から選択モードに戻ることができるので、選択モードでゲート位置を適宜調整されたい。また、"Edit → Mirror", "Edit → Rotate" からゲートを回転、反転させることもできるので、適宜使用されたい。

図8. シンボル選択画面 (パネル)

次に入出力マーカ、ゲート間を配線する。"Add → Wire" により配線モードになる。始点と終点をクリックすることにより配線を引くことができる。

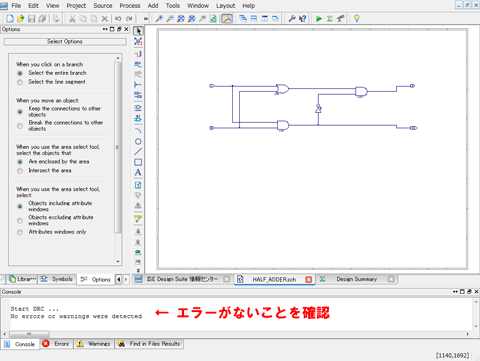

最後に "Tools → Check Schematics" により、回路図にエラーがないか確認する。トランスクリプト窓に "No error or warning is detected" と出力されれば検証成功である。図9 は記述した半加算器に対し検証を行った直後の画面である。見にくいが、トランスクリプト窓にエラーが無い旨が表示されている。"File → Save" で作成した回路を保存する。

図9. 半加算器に対する検証結果例

なお、回路図はワークスペース中のシート(灰色の枠)内に作成しなければならない。シートの大きさを変更したいときは、選択モードから、何も選択せずに "Edit → Object Properties" とする。図10 のようなダイアログが開くので、Size 列を変更するとよい。

作成した回路は期待通りの動作をしているか、シミュレーション実験によって検証される必要がある。ここでは先に作成した HALF_ADDER を題材に、シミュレーション実験の方法について説明する。

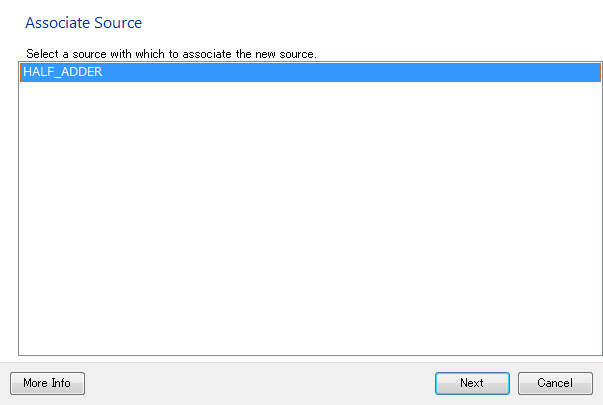

シミュレーション実験においては、作成した回路に検証用入力データを与える必要がある。検証用入力データは検証用モジュールより与えられる。検証用モジュール testbench の作成手順を以下に説明する。まず、シミュレーション実験用モジュールを以下の手順で作成する。New Source Wizard を起動し、ソースタイプ (図5の左側で指定) は "Verilog Test Fixture"、File Name は "testbench" とする。続いて、図11 のように Associate Source ダイアログが開くので、検証したいモジュールである "HALF_ADDER" を選ぶ。

図11. 検証対象モジュールの選択

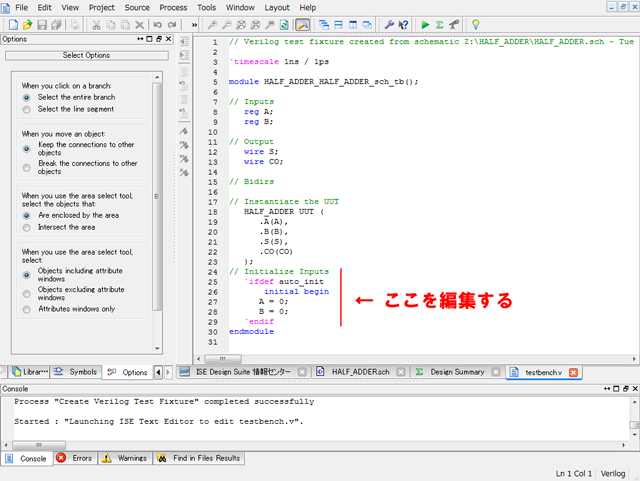

その後、肯定的な回答を繰り返すと、図12 のようにワークスペースのタブ testbench.v に、検証用モジュールのプログラムエディタが起動する。

図12. 検証用モジュールエディット画面

" // Initialize Inputs " という行より後を図13 の通りに編集、保存して欲しい。なお、Wizard が出力する `ifdef 文、`endif文は削除する必要があることに注意されたい。

// Initialize Inputs

initial begin

A = 0; B = 0; #10

A = 1; B = 0; #10

A = 0; B = 1; #10

A = 1; B = 1; #10

$finish;

end

endmodule

|

図13. HALF_ADDER 用検証モジュール (最後の一部分)

シミュレーションはシミュレータ ISim 上で行われる。ISim は ISE から呼び出される。状況によって ISim 実行時にプログラム isimgui.exe がファイアウォールでブロックされることがある。この場合はキャンセルを選び、無視すればよい。

まず、ISim 起動前に検証用モジュールの文法チェックを行う。パネルのタブを "Design" とし、図14 のように、(1) View に "Simulation" を選択、(2) Hierarchy に "HALF_ADDER_HALF_ADDER_sch_tb (testbench.v)" を選択する。続いて、(3) Processes から "ISim Simulator → Behavioral Check Syntax" とする。検証用モジュールの文法チェックがなされ、図14 のように、チェック結果がプロセスにアイコンで表示されると同時に、トランスクリプトに詳細結果が表示される。図のように緑のレ印が出た場合は文法チェックに成功している。赤い×印が出た場合は、文法エラーがある。トランスクリプト窓のエラーメッセージを参考にし、図 13 と見比べながら修正すること。

図14. シミュレータ ISim 起動直前の画面

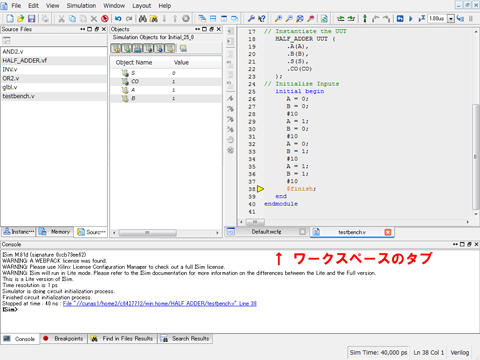

続いて、図14 (3) Processes から "Simulate Behavioral Model" とする。シミュレータ ISim が起動し、図15 のような画面が表示される。

図15. ISim 起動直後の画面

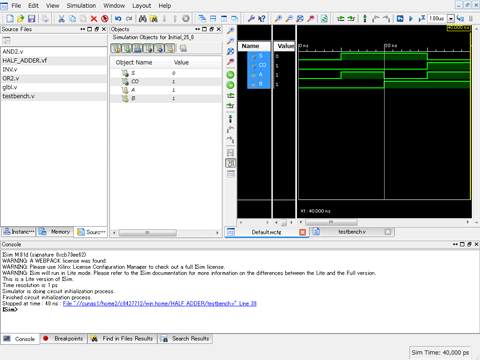

ISim もまた、ISE 同様ワークスペースを持つ。シミュレーション結果はワークスペースのタブ "Default.wcfg" に得られているので、これを選択する。図16 のようにシミュレーション結果が得られるはずである。おそらくズームがあっていないはずである。 " View → Zoom → To Full View" とし、ズームを合わせること。

シミュレーション結果中、折れ線は、高い位置にあるとき、信号線の値が 1、低い位置にあるとき 0 であることを示している。入力 A, B の値と出力 CO, S の値の関係がが表1 の真理値表と一致することを確認すること。

図16. シミュレーション結果

続いて、図13 に示した検証用モジュールの意味について説明する。このプログラムは "initial begin" から "end" までの間実行される。それぞれ "A = x; B = y;" は A に x, Y に y を代入するという意味である。また、"#t" は t ns 時間を進めるという意味である。"$finish" はシミュレーションを終了するという意味である。図13 とシミュレーション結果をよく見比べ、また検証用モジュールを適宜修正してみて、理解すること。

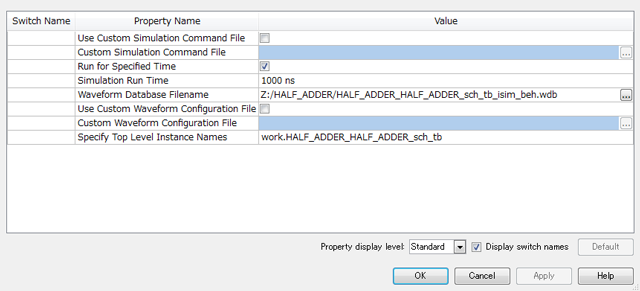

時間 t の値を大きくしたとき、1000 ns より長くシミュレーションできないことに気づいたかも知れない。図14 (3) Processes 中 "Simulate Behavioral Model" を右クリックし、"Process Proterties" を選択して欲しい。図17 のようなダイアログが現れる。"Simulation Run Time" が 1000 ns に指定されている。これを変更することにより、最長のシミュレーション時間を変更することができる。

図17. シミュレーションプロセスプロパティ

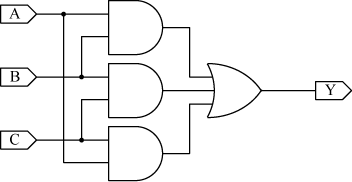

3入力多数決回路をシミュレーションで動作確認せよ。3入力多数決回路の回路図と真理値表を図18と表2に示す。3入力多数決回路は3入力値について多数決を取り、その結果を出力する。

図18. 3入力多数決回路の回路図

表2. 3入力多数決回路の真理値表

| A | B | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 |

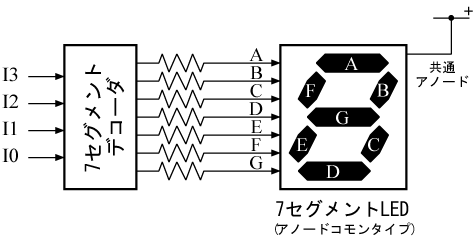

入力I3〜I0の値に応じ、15のように8の字型に並べられた7つの発光ダイオード(7セグメントLED)を10進表示するように制御する回路が7セグメントデコーダである。ここで、I3〜I0 の値とは、これらの値を2進表記された数値、すなわち23×I3+22×I2+21×I1+20×I0 であると解釈した値である。7セグメントデコーダを設計し、シミュレーションで動作確認せよ。なお設計する回路は正論理である(つまり電圧レベルが高いときを1、低いときを0とする)と仮定せよ。

図19. 7セグメントデコーダと7セグメントLED

【参考】7セグメントLEDの表示を模倣する検証用モジュールについて

難波 一輝 (助教・伊藤・北神・難波研究室)

工学部1号棟4階409号室、内線3255、043-290-3255、namba@ieee.org