��1. �ޥ���ץ쥯����ϩ

"��ϩ���ߥ�졼���ˤĤ���" �ͤˤ��ʤ���Ⱦ�û�������û�����Ф��륷�ߥ�졼�����¸���»ܤ��衣

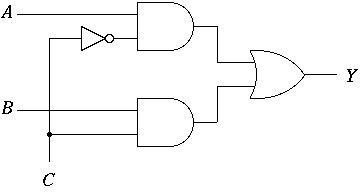

��1�β�ϩ(�ޥ���ץ쥯����ϩ)�� Verilog-HDL �ǵ��Ҥ��衣�ޤ������β�ϩ�ε�ǽ���������衣������ A, B, C �����Ͽ���Ǥ��ꡢY �Ͻ��Ͽ���Ǥ��롣����ˡ����Ҥ�����ϩ���Ф����ߥ�졼�����¸���»ܤ��衣

��1. �ޥ���ץ쥯����ϩ

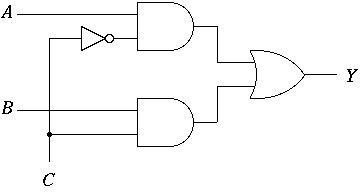

��2�Τ褦��Ⱦ�û���1�Ĥ����û���3�Ĥ��Ȥ߹�碌��4�ӥåȲû����Verilog-HDL�dz��ز��߷פ������ߥ�졼������ư���ǧ���衣�����Ⱦ�û�����û���ε��Ҥϼ¸��ƥ����Ȥͤˤ��衣

��2. 4�ӥåȲû���ϩ

4�ӥå�������A (�����ѥ�ƥ����) �γ������ͤˤ�����1�ο�������ΤȤ����ϥӥå�E��1����Ϥ���1�ο��������λ����ϥӥå�E��0����Ϥ���ѥ�ƥ������å���Verilog-HDL���߷פ��衣

ɽ1. �ѥ�ƥ������å�������ɽ

|

|

����5�ʹߤ�����٤��⤤��;�ϤΤ���ԤΤ�ĩ�路���ߤ�����

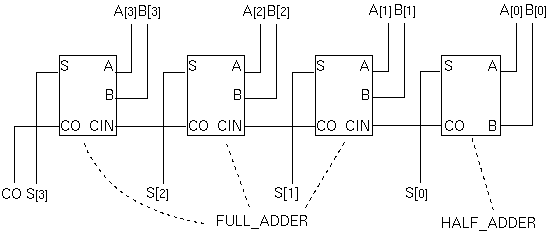

������I���ͤ˱�������3�Τ褦��8�λ������¤٤�줿7�Ĥ�ȯ������������(7��������LED)��10��ɽ������褦�����椹���ϩ��7�������ȥǥ������Ǥ��롣7�������ȥǥ�������Verilog-HDL���߷פ������ߥ�졼������ư���ǧ���衣�ʤ��߷פ����ϩ���������Ǥ���(�Ĥޤ��Ű���٥뤬�⤤�Ȥ���1���㤤�Ȥ���0�Ȥ���)�Ȳ��ꤻ�衣

��3. 7�������ȥǥ�������7��������LED

�ڻ��͡�7��������LED��ɽ�������魯�븡���ѥ⥸�塼��ˤĤ���

(7,4) �ϥߥ�������沽�������Verilog-HDL���߷פ������ߥ�졼������ư���ǧ���衣������ (7,4) ���Ȥ������Ĺ����7�ӥåȡ�������Ĺ����4�ӥåȤ�������

4�ӥåȾ軻���Verilog-HDL���߷פ������ߥ�졼������ư���ǧ���衣

���� �쵱 (��������ƣ���̿������ȸ��漼)

������1����4��409�漼������3255��043-290-3255��namba@ieee.org