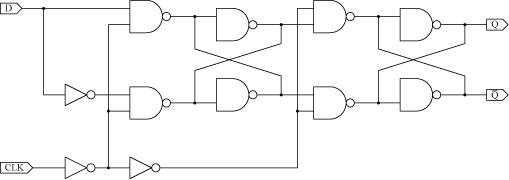

図1. Dフリップフロップの回路図

先週の実験では、Verilog を用いて組合せ回路を設計した。今週は順序回路の設計を学ぶ。また、複雑な順序回路設計を体験する。

Dフリップフロップはクロック信号線が立ち上がった(0から1へ変化した)瞬間の入力D の値を記憶する記憶素子である。Dフリップフロップの回路図を図1に示す。

図1. Dフリップフロップの回路図

Verilog において Dフリップフロップを記述したいとき、この回路図をそのまま assign 文で記述してはいけない。Verilog においてフリップフロップは手続きブロックを用いて記述される。図2 に Dフロップフロップの記述例を示す。

module D_FLIPFLOP(D, CLK, Q);

input D;

input CLK;

output Q;

reg Q;

always@(posedge CLK) begin

Q <= D;

end

endmodule

|

図2. Dフリップフロップの Verilog記述

入力信号値が変化した瞬間に出力信号値が変化する組合せ回路においては always に続く @(〜)には * 印を記述した。一方、クロックが立ち上がった瞬間にのみ出力値が更新されるフリップフロップを記述するときは、@(〜)にはキーワード posedge とクロック信号名を記述する。

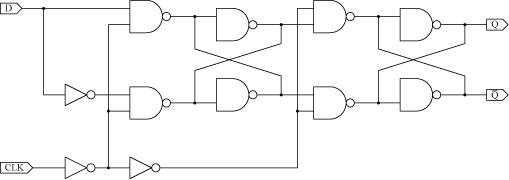

図2の回路をシミュレーション実験で動作検証する。"Initialize Timing and Clock Wizard" において Clock Information は図3 のように Single clock とし、クロック入力 CLK を指定すること。

図3. クロックウィザードにおけるクロック入力の指定

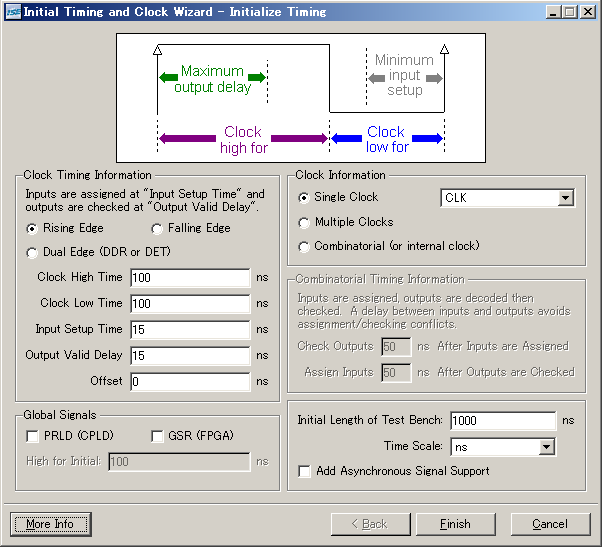

図4に示すような波形エディタが起動する。クロック信号 CLK の波形は既にウィザードによって作成されているので入力信号 D だけ作成すればよい。

図4. クロック信号を有する回路に対する波形エディタ

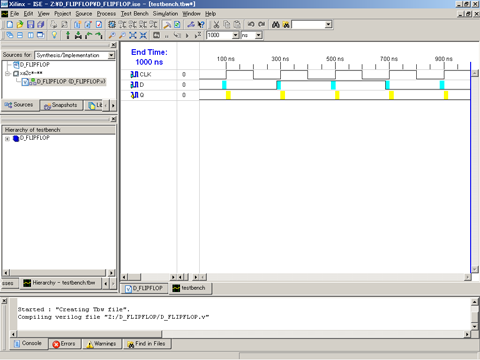

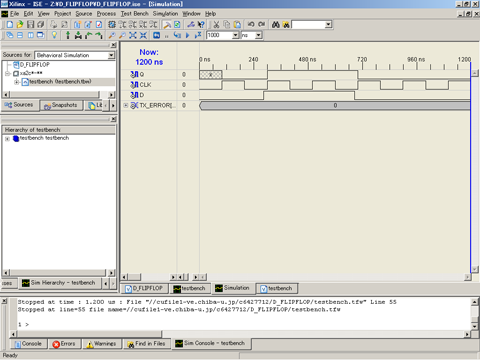

図5にDフリップフロップに対するシミュレーション結果例を示す。クロックが立ち上がった瞬間に出力 Q の値が入力 D の値によって更新されている。シミュレーション開始直後から最初のクロック立ち上がり時まで、つまり0ns〜100nsにおいて、出力 Q の値がメッシュで表示されている。これは出力値 Q が不定値であることを意味しており、フリップフロップの値が初期化されていないことに起因している。

図5. Dフリップフロップのシミュレーション結果

先週の組合せ回路の場合と同様、手続きブロックの中には if, case などを用いた複雑な処理を書くことができる。図6は長さ4ビットのシフトレジスタの記述例である。リセット信号 RST が 1 のとき、シフトレジスタの値は全零にリセットされる。RST が 0 のとき、値がシフトする。ただし、値の更新はクロック入力 CLK が立ち上がった瞬間にのみ行われる。

module SHIFT_REGISTER(IN, CLK, RST, OUT);

input IN;

input CLK;

input RST;

output [3:0] OUT;

reg [3:0] OUT;

always@(posedge CLK) begin

if(RST) begin

OUT <= 4'b0000;

end else begin

OUT <= {OUT[2:0], IN};

end

end

endmodule

|

図6. 4ビットシフトレジスタの Verilog記述

リセット信号付き 5進カウンタを Verilog で記述せよ。

2課題を用意した。難易度に大きな差はない。好きな方を選択して実施せよ。

難波 一輝 (助教・伊藤・北神・難波研究室)

工学部1号棟4階409号室、内線3255、043-290-3255、namba@ieee.org