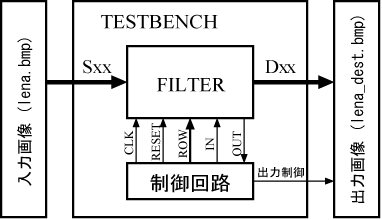

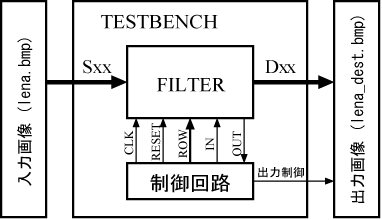

図1. サンプルプログラムの回路図

ここでは 32x32 モノクロ画像を加工するフィルタ回路を設計し、シミュレータ上で動作させる。サンプルプログラムと画像を用意したのでダウンロードすること。

ダウンロードしたアーカイブに含まれるファイル filter.v と testbench.v はサンプルプログラムであり、サンプル画像 lena.bmp を白黒反転し、その結果を lena_dest.bmp に出力する。回路図を図1に示す。この回路はファイル testbench に記述されたモジュール TESTBENCH からなる。TESTBENCH はモジュール FILTER を含む。モジュール FILTER は filter.v に記述される。

図1. サンプルプログラムの回路図

画像 lena.bmp は 32x32 の画像であり、モジュール FILTER には各クロック毎に1行32画素が入力 S00 〜 S31 より入力される。また、加工(白黒反転)された画像が1行毎に出力 D00 〜 D31 より出力される。ここで、Si, Di はそれぞれ左から i 番目の画素であり、0〜255 の 256調である。

モジュール FILTER は TESTBENCH 内に設けられた制御回路から与えられる制御信号によって制御される。RESET はリセット信号であり、シミュレーション開始直後は 1、まもなく 0 となり、シミュレーション終了まで 0 であり続ける。IN が 1 のとき、FILTER に画像が入力される。このとき、i 行目の画像が入力されているなら、ROW の値は i となる。画像は32クロック連続して入力される。全ての行を入力し終えたら IN は 0 となる。OUT は FILTER から出力される制御信号である。OUT が 1 のとき、FILTER から画像が出力される。 OUT が 32 回 1 を出力したとき、シミュレーションは終了する。なお、このプログラムは bmp 形式のデータ出現順通り、最下行から上へと順に処理を行う。

シミュレーションは以下の手順で行うことができる。まずは、プロジェクトを作成し、プロジェクトに filter.v と testbench.v を加える。続いてサンプル画像 lena.bmp を作成したプロジェクトのディレクトリにコピーする。シミュレーションを実行する。このとき、シミュレーションは 1000ns で途中停止する。そこで "Simulation → Run All" とし、シミュレーションを最後まで実行する。プロジェクトのディレクトリに白黒反転された画像ファイル lena_dest.bmp が作成されているはずである。

以下の課題では白黒反転フィルタ以外の処理を行う回路を作成する。基本的にモジュール FILTER にのみ手を加えればよく、testbench.v にはサンプル画像名以外に手を加える必要はない。また、FILTER のモジュール名、入出力名、バス幅を変更してはいけない。FILTER の出力値はクロックと同期させて変化させる必要がある。

OUT=1 が 32回出力されない限りシミュレーションは終了しない。よって、OUT が適切に変化しない FILTER を作成したとき、シミュレーションは永遠に終わらない。"Running simulation. Simulation time 〜 "と表示されたときは、"Simulation → Stop" とし、速やかにシミュレーションを強制的に終了すること。強制終了時までのシミュレーション結果が表示されるので、デバッグ時の参考とされたい。

難波 一輝 (助教・伊藤・北神・難波研究室)

工学部1号棟4階409号室、内線3255、043-290-3255、namba@ieee.org