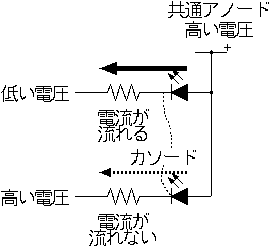

発光ダイオードはアノード(陽極)とカソード(陰極)を持ち、アノードに高い電圧、カソードに低い電圧をかけたときのみ電流が流れ発光する。アノードコモン7セグメントレジスタは図1に示すようにアノードが共通となっている。使用時には共通アノードに常時高い電圧をかける。カソードは各ダイオード毎別々になっており、カソード側(カソードに接続する抵抗)にかける電圧によって、ダイオードが発光するかどうか決まる。カソード側に共通アノードと同じく高い電圧をかけたとき、電圧が等しいため、電流は流れない、つまり発光しない。カソード側に低い電圧をかけたとき、電流が流れ、ダイオードが発光する。以上より、7セグメントデコーダは発光させたいダイオードに対応する出力の電圧を低くする(つまり、論理値0にする)必要がある。

|

| 図1. 発光ダイオードと電圧 |

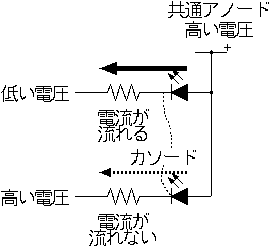

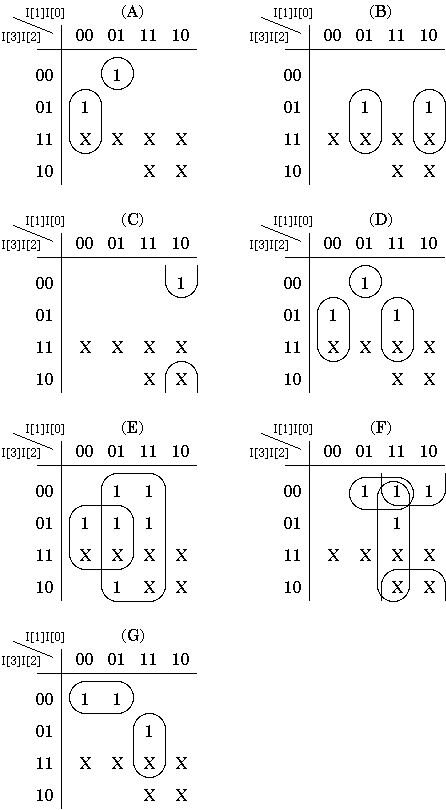

表2に7セグメントデコーダの真理値表を示す。また、真理値表に基づいて作成したカルノー図を図2に示す。

| 表2. 7セグメントデコーダの真理値表 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| 図2. 7セグメントデコーダのカルノー図 |

カルノー図に基づいて作成した7セグメントデコーダを以下に示す。

module DECODER7 (I, A, B, C, D, E, F, G);

input [3:0] I;

output A, B, C, D, E, F, G;

assign A = ~I[3] & ~I[2] & ~I[1] & I[0] | I[2] & ~I[1] & ~I[0];

assign B = I[2] & ~I[1] & I[0] | I[2] & I[1] & ~I[0];

assign C = ~I[2] & I[1] & ~I[0];

assign D = ~I[3] & ~I[2] & ~I[1] & I[0] | I[2] & ~I[1] & ~I[0] |

I[2] & I[1] & I[0];

assign E = I[0] | I[2] & ~I[1];

assign F = ~I[2] & I[1] | I[1] & I[0] | ~I[3] & ~I[2] & I[0];

assign G = ~I[3] & ~I[2] & ~I[1] | I[2] & I[1] & I[0];

endmodule

|

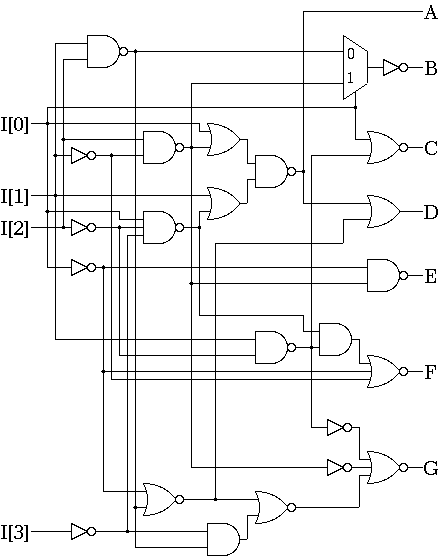

本実験で扱っている verilog 記述は RTL レベル (Register Transfer Level) と呼ばれるレベルの記述法であり、回路とは一対一の関係を取っていない。実際の設計工程では、RTL レベルで回路を設計した後、論理合成ツールを用いて論理合成を行い、回路と一対一の対応が取れるゲートレベル(ネットリストレベル)の記述へ変換する。この際、論理合成ツールは、伝搬遅延時間やコンデンサの容量など、さまざまな要因を考慮しながら、また、なるべく面積が小さくなるよう、実際に使用するゲートを選択する。本実験では、RTL レベル記述とはいえ、まだ回路構成がはっきり見える記述のみを扱った。しかし、実際の RTLレベル記述では、回路構成が見えない記述も可能である。例えば真理値表をそのまま記述することも可能である。この場合、人間がカルノー図を書かなくても、論理合成ツールが回路構成を自動生成してくれる。例として課題5で扱った7セグメントデコーダについて、真理値表から論理合成ツールに生成させた回路を図4に示す。

|

| 図4. 論理合成ツールが生成した7セグメントデコーダ |

論理合成ツールを用いることにより、いちいちカルノー図などを書く手間が省ける他、人間でもなかなか思いつけないような回路量の小さい回路構成を得ることができる。回路設計者はゲートレベルの様々な細かい問題をいちいち強く意識する必要がなく、大局的な視点からの回路設計に専念することができる。もっとも現状では、より良い回路を得るためにはゲートレベルの問題もいくらか意識しながら設計した方がよい。

合成技術の発展はめざましく、近年では C/C++ 等で書かれたプログラム、つまりクロック信号など回路の構成に必要な事柄を考慮せずに組まれたプログラムを、タイミング、スケジューリング等の問題を解決しながら RTLレベルやゲートレベルに変換する高位合成の開発研究も進んでいる。

難波 一輝 (助教・伊藤・北神・難波研究室)

工学部1号棟4階409号室、内線3255、043-290-3255、namba@ieee.org